## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2020/0185481 A1 PARK et al.

Jun. 11, 2020 (43) **Pub. Date:**

### (54) ORGANIC LIGHT EMITTING DIODE DISPLAY

### (71) Applicant: SAMSUNG DISPLAY CO., LTD., Yongin-Si (KR)

## (72) Inventors: JUN HYUN PARK, Suwon-Si (KR);

Kang Moon Jo, Hwaseong-Si (KR); Dong Woo Kim, Yongin-Si (KR); Sung Jae Moon, Seongnam-Si (KR); An Su Lee, Seoul (KR); Woong-Sik Choi,

Suwon-Si (KR)

(21) Appl. No.: 16/698,121

(22)Filed: Nov. 27, 2019

#### Foreign Application Priority Data (30)

| Dec. 7, 2018  | (KR) | 10-2018-015  | 7411  |

|---------------|------|--------------|-------|

| Dec. 20, 2018 | (KR) | 10-2018-0166 | 54 77 |

#### **Publication Classification**

(51) Int. Cl. H01L 27/32 (2006.01)

U.S. Cl. (52)

> H01L 27/3265 (2013.01); H01L 27/3248 (2013.01); H01L 27/1225 (2013.01); H01L 27/3276 (2013.01); H01L 27/3262 (2013.01)

#### ABSTRACT (57)

According to an exemplary embodiment, an organic light emitting diode display includes: a substrate; a semiconductor layer; a first gate insulating layer disposed on the oxide semiconductor layer; a first gate layer disposed on the first gate insulating layer; a first interlayer insulating layer disposed on the first gate layer; a first data layer disposed on the first interlayer insulating layer; a second interlayer insulating layer disposed on the first data layer; a driving voltage line and a driving low voltage line disposed on the second interlayer insulating layer and separated from each other; an upper insulating layer covering the driving voltage line and the driving low voltage line; and an anode disposed on the upper insulating layer and overlapping the driving voltage line or the driving low voltage line.

FIG. 1

FIG. 2

FIG. 3

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

XX |XX 8 185 155

# ORGANIC LIGHT EMITTING DIODE DISPLAY

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] This U.S. non-provisional application claims the benefit of priority under 35 U.S.C. § 119 to Korean Patent Applications Nos. 10-2018-0157411 and 10-2018-0166477 filed in the Korean Intellectual Property Office on Dec. 7, 2018 and Dec. 20, 2018, respectively, the entire disclosures of which are incorporated by reference herein.

### **BACKGROUND**

### (a) Technical Field

[0002] The present disclosure relates to an organic light emitting diode display, and more particularly, to an organic light emitting diode display with a high resolution.

### (b) Discussion of Related Art

[0003] Display devices are devices that display images. A flat panel display is a television, monitor or other display device that uses a thin panel design instead of a traditional cathode ray tube (CRT) design. Examples of flat panel displays include an organic light emitting diode (OLED) display and a liquid crystal display.

[0004] Since an organic light emitting diode display has a self-emission characteristic and does not require a separate light source, the organic light emitting diode display can be thinner and lighter than a liquid crystal display device. Further, the organic light emitting diode display may consume less power, have a higher luminance and have a higher response speed than a liquid crystal display.

[0005] However, since the organic light emitting diode (OLED) display has a more complicated pixel structure than a liquid crystal display, and it is difficult to provide a space for forming the pixel as the resolution increases.

### **SUMMARY**

[0006] At least one exemplary embodiment of the inventive concept provides an organic light emitting diode display with a high resolution, in which a capacitance of a storage capacitor connected to one terminal of a driving transistor is increased.

[0007] According to an exemplary embodiment of the inventive concept, an organic light emitting diode display includes: a substrate; a semiconductor layer; a first gate insulating layer disposed on the oxide semiconductor layer; a first gate layer disposed on the first gate insulating layer; a first interlayer insulating layer disposed on the first gate layer; a first data layer disposed on the first interlayer insulating layer; a second interlayer insulating layer disposed on the first data layer; a driving voltage line and a driving low voltage line disposed on the second interlayer insulating layer and separated from each other; an upper insulating layer covering the driving voltage line and the driving low voltage line; and an anode disposed on the upper insulating layer and overlapping the driving voltage line or the driving low voltage line.

[0008] The driving voltage line and the driving low voltage line may extend in a longitudinal direction.

[0009] The anode may be electrically connected to an anode connection part formed to be separated from the driving voltage line and the driving low voltage line on a same layer.

[0010] In an embodiment, the organic light emitting diode display includes a plurality of pixels and the anode is disposed in each of the pixels.

[0011] A part of the anode may overlap the driving voltage line, and another part of the anode may overlap the driving low voltage line.

[0012] The anode connection part may be disposed between the driving voltage line and the driving low voltage line

[0013] The anode may overlap the driving voltage line.

[0014] The driving voltage line may have an anode connection part opening corresponding to the anode connection part, and the anode connection part is disposed within the anode connection part opening.

[0015] In an exemplary embodiment, the organic light emitting diode display further includes an overlapping layer disposed between the substrate and the semiconductor layer, the overlapping layer including a channel overlapping part overlapping a channel of a first transistor and an extension part extended from the channel overlapping part, and the extension part of the overlapping layer overlaps a first gate electrode of the first transistor to form an overlapping capacitor.

[0016] The driving voltage line may have a parasitic capacitor opening so that the anode forms a parasitic capacitance with the first gate insulating layer or the first data layer.

[0017] In an exemplary embodiment, the organic light emitting display includes an organic emission layer disposed on the anode and a cathode disposed on the organic emission layer, the cathode is electrically connected to a cathode connection part disposed on a same layer as the anode, and the cathode connection part is electrically connected to the driving low voltage line.

[0018] In an exemplary embodiment, the driving voltage line has a larger width than the anode, and the driving low voltage line has a width that is larger than half of the width of the anode.

[0019] In an exemplary embodiment, the first gate layer includes a pair of scan lines receiving a same scan signal, the first data layer includes a pair of data lines connected to one pixel column, among two adjacent pixels included in the one pixel column, one pixel is connected to one scan line of the pair of scan lines and one data line of the pair of data lines, and the other pixel is connected to the other scan line of the pair of scan lines and the other data of the pair of data lines. [0020] An organic light emitting diode display according to an exemplary embodiment of the inventive concept includes: a substrate; a semiconductor layer disposed on the substrate; a first gate insulating layer disposed on the semiconductor layer; a first gate layer disposed on the first gate insulating layer; a second gate insulating layer disposed on the first gate layer; a second gate layer disposed on the second gate insulating layer; a first interlayer insulating layer disposed on the second gate layer; a first data layer disposed on the first interlayer insulating layer and including a data line, an initialization voltage line, a driving voltage line, and a driving low voltage line; an upper insulating layer covering the first data layer; and an anode disposed on the

upper insulating layer, wherein the anode includes an addi-

tional capacitor extension part, and the additional capacitor extension part overlaps the driving low voltage line.

[0021] In an exemplary embodiment, the organic light emitting diode display further includes an overlapping layer disposed between the substrate and the semiconductor layer, and the overlapping layer overlaps a channel of a first transistor.

[0022] In an exemplary embodiment, the driving voltage line and the driving low voltage line are adjacently disposed, and the width of the driving low voltage line is wider than the width of the driving voltage line.

[0023] The driving low voltage line may also overlap the driving voltage line.

[0024] In an exemplary embodiment, the organic light emitting diode display includes a second interlayer insulating layer disposed between the first data layer and the upper insulating layer and a second driving low voltage line disposed between the first data layer and the upper insulating layer. In this embodiment, the second interlayer insulating layer is disposed on the first data layer, the second driving low voltage line is disposed on the second interlayer insulating layer, and the driving low voltage line is electrically connected to the second driving low voltage line to transmit the driving low voltage through a dual structure.

[0025] In an exemplary embodiment, the organic light emitting diode display includes a cathode connection part disposed on a same layer as the anode and electrically connected to the driving low voltage line, and the additional capacitor extension part of the anode is disposed and separated from the cathode connection part.

[0026] In an exemplary embodiment, the organic light emitting diode display includes a plurality of pixels, the anode is disposed in each of the pixels, and at least one anode does not include the additional capacitor extension part.

[0027] An organic light emitting diode display according to an exemplary embodiment of the inventive concept includes: a substrate; a semiconductor layer disposed on the substrate; a first gate insulating layer disposed on the semiconductor layer; a first gate layer disposed on the first gate insulating layer; a second gate insulating layer disposed on the first gate layer; a second gate layer disposed on the second gate insulating layer; an interlayer insulating layer disposed on the second gate layer; a data layer disposed on the interlayer insulating layer and including a data line and a driving voltage line; an upper insulating layer disposed on the data layer; and an anode disposed on the upper insulating layer and completely covering the gate electrode of a first transistor disposed on the first gate layer, wherein the anode overlaps the driving voltage line to form an additional capacitor.

$[0\bar{0}28]$  The driving voltage line may extend in a longitudinal direction.

[0029] One side of the anode extending in the longitudinal direction may overlap the driving voltage line.

[0030] In an exemplary embodiment, the semiconductor layer include a first semiconductor, a second semiconductor, and a third semiconductor, the first transistor is disposed on the first semiconductor, a second transistor is disposed on the second semiconductor, and a third transistor is disposed on the third semiconductor.

[0031] At least one of the first semiconductor, the second semiconductor, and the third semiconductor may include an opening.

[0032] The first semiconductor may include a channel region, a source region, and a drain region, and the source region may overlap the anode and the driving voltage line.

[0033] The organic light emitting diode display may further include an overlapping layer disposed between the substrate and the semiconductor layer.

[0034] The overlapping layer may include a channel overlapping part overlapping the channel region of the first semiconductor and an extension part extending from the channel overlapping part, and the extension part of the overlapping part may overlap the gate electrode of the first transistor.

[0035] The second gate layer may include a storage electrode, the gate electrode of the first transistor and the storage electrode may overlap to form a storage capacitor, and the storage capacitor may completely overlap the anode.

[0036] The overlapping layer may be connected to the storage electrode through an opening, and the storage electrode may be electrically connected to the anode through the connection part formed in the data layer.

[0037] The second semiconductor may include a channel region, a source region, and a drain region, and the source region may overlap the data line to be electrically connected thereto.

[0038] In an exemplary embodiment, the organic light emitting diode display includes a transverse driving voltage line included in the first gate layer and extending in a horizontal direction crossing the driving voltage line.

[0039] In an exemplary embodiment, the organic light emitting diode display includes a plurality of pixels and the transverse driving voltage line is electrically connected to at least one pixel among the pixels adjacent in a row direction.

[0040] In an exemplary embodiment, the organic light emitting diode display includes an initialization voltage line included in the data layer and extending in a longitudinal direction

[0041] In an exemplary embodiment, the organic light emitting diode display includes a plurality of pixels and an initialization voltage transmitting part disposed in a horizontal direction crossing the initialization voltage line, and the initialization voltage transmitting part is electrically connected to at least one pixel among the pixels adjacent in the row direction.

[0042] In an exemplary embodiment, the organic light emitting diode display further includes a driving low voltage line included in the data layer and extending in a longitudinal direction.

[0043] In an exemplary embodiment, the semiconductor layer includes a first semiconductor, a second semiconductor, and a third semiconductor, the first transistor is disposed on the first semiconductor, the second transistor is disposed on the second semiconductor, and the third transistor is disposed on the third semiconductor and the anode overlaps the first semiconductor, the second semiconductor, and the third semiconductor.

[0044] The first gate layer may further include a scan line and a previous scan line extending in a horizontal direction.

[0045] The first gate layer may include a gate electrode of the third transistor, and the gate electrode of the third transistor may be electrically connected to the previous scan line through a connection part included in the second gate layer and a connection part included in the data layer.

[0046] The organic light emitting diode display may further include an organic emission layer disposed on the anode and a cathode disposed on the organic emission layer.

[0047] According to exemplary embodiments, in an organic light emitting diode display with high resolution, the driving voltage line applying the driving voltage or the driving low voltage line applying the driving low voltage are formed to overlap the anode to form the additional capacitor, thereby having sufficient capacitance in a narrow area.

[0048] Also, by forming the driving low voltage line with the dual-layered structure, a voltage drop generated when applying the driving low voltage may be eliminated.

[0049] Further, as the capacitance of the storage capacitor connected to one end of the driving transistor is increased, the display quality of the display device may be improved. [0050] According to an exemplary embodiment, since the anode does not overlap the data line, crosstalk due to parasitic capacitance with the data line may be reduced.

### BRIEF DESCRIPTION OF THE DRAWINGS

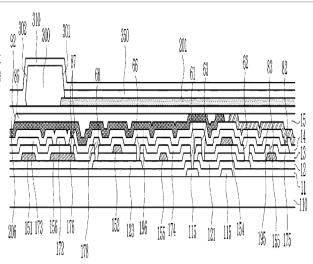

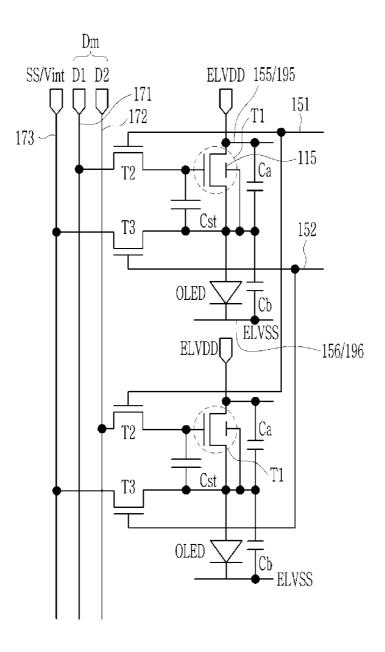

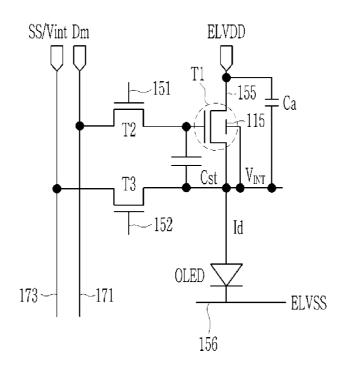

[0051] FIG. 1 is an equivalent circuit diagram of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept.

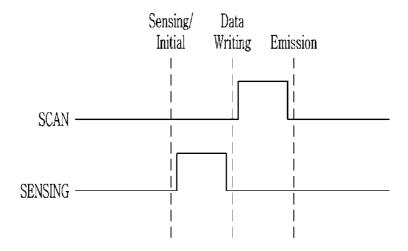

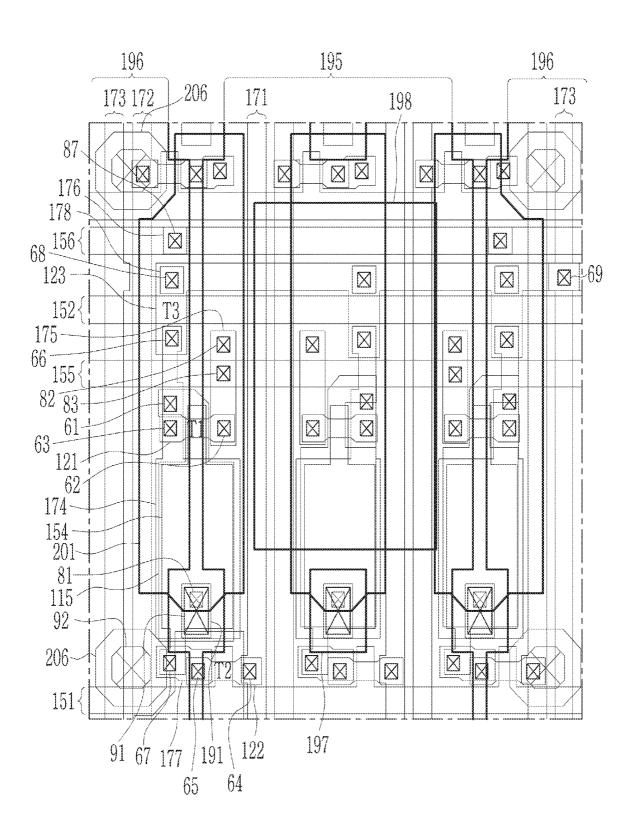

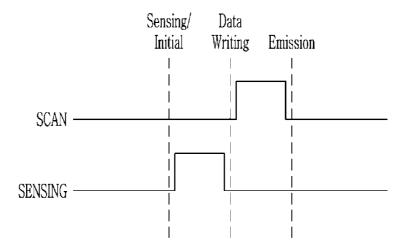

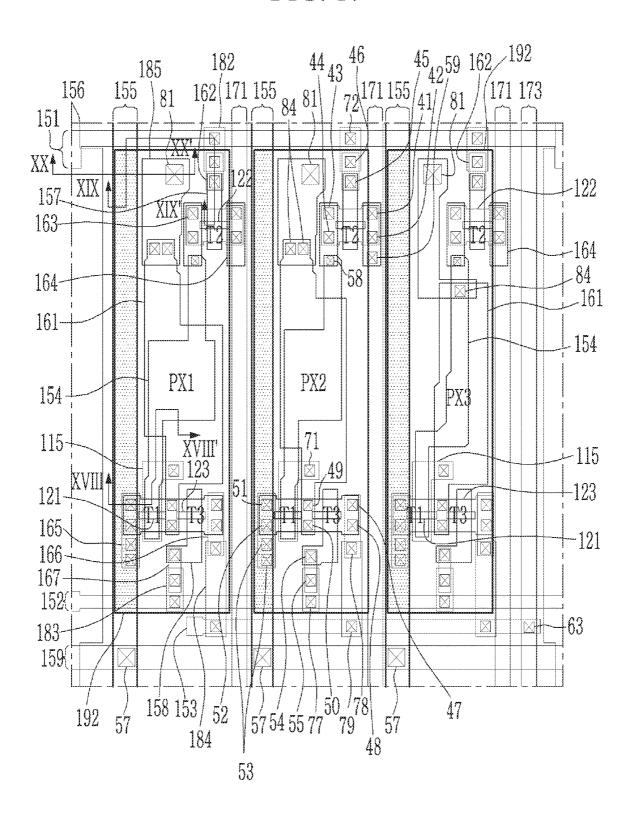

[0052] FIG. 2 is a timing diagram of a signal applied to one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept. [0053] FIG. 3 is a layout view of a region of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept.

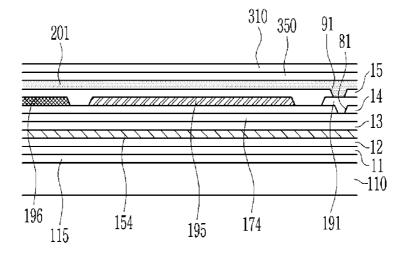

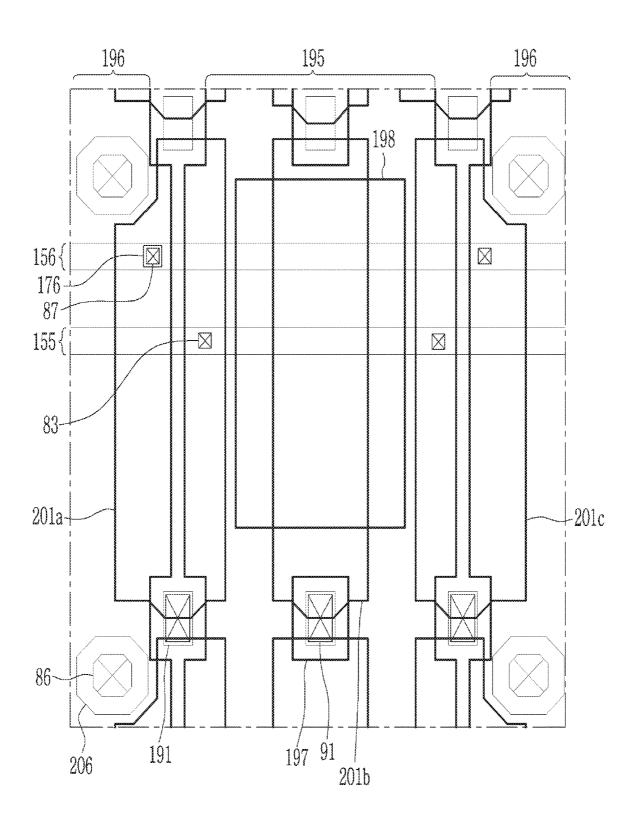

[0054] FIG. 4 and FIG. 5 are a cross-sectional view taken along lines IV-IV and V-V in an exemplary embodiment of FIG. 3.

[0055] FIG. 6 is a layout view showing only a specific layer among one pixel of an organic light emitting diode display according to an exemplary embodiment of FIG. 3. [0056] FIG. 7 is a layout view of a region of one pixel of an organic light emitting diode display according to another exemplary embodiment of the present inventive concept.

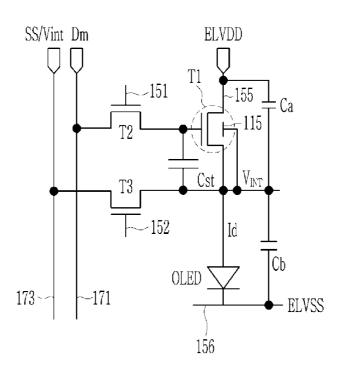

[0057] FIG. 8 is a layout view showing only a specific layer among one pixel of an organic light emitting diode display according to an exemplary embodiment of FIG. 7. [0058] FIG. 9 is an equivalent circuit diagram of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept.

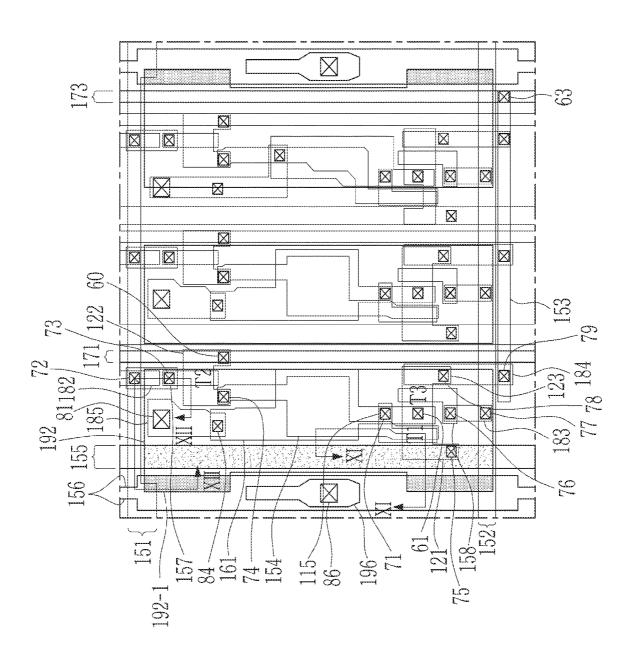

[0059] FIG. 10 is a layout view of a region of one pixel of an organic light emitting diode display according to an exemplary embodiment of the present inventive concept.

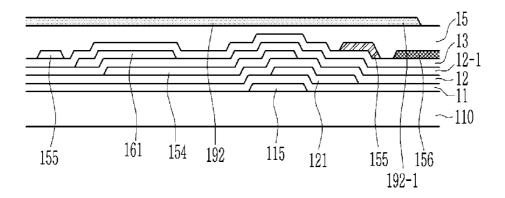

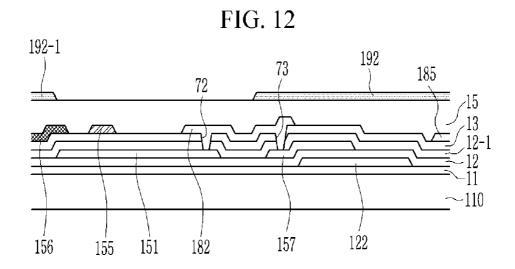

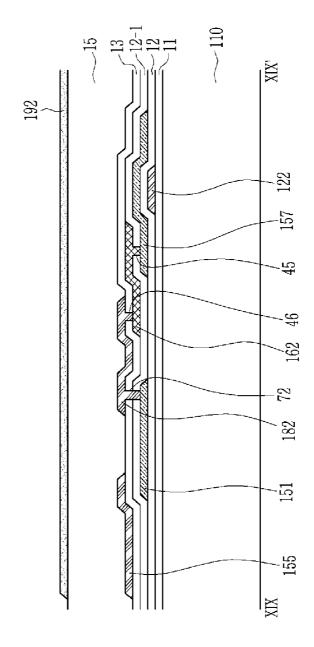

[0060] FIG. 11 and FIG. 12 are a cross-sectional view taken along lines XI-XI and XII-XII in an exemplary embodiment of FIG. 10.

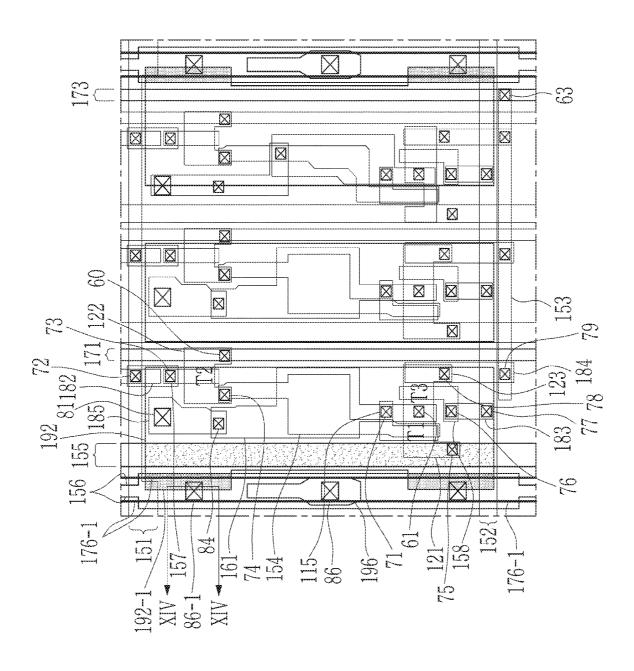

[0061] FIG. 13 is a layout view of a region of one pixel of an organic light emitting diode display according to an exemplary embodiment of the present inventive concept.

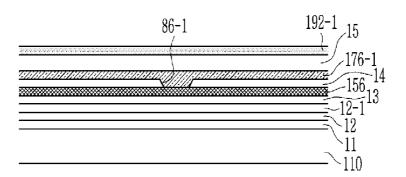

[0062] FIG. 14 is a cross-sectional view taken along a line XIV-XIV in an exemplary embodiment of FIG. 13.

[0063] FIG. 15 is an equivalent circuit diagram of one pixel of an organic light emitting diode display of one pixel according to an exemplary embodiment of the present inventive concept.

[0064] FIG. 16 is a timing diagram of a signal applied to one pixel of an organic light emitting diode display according to an exemplary embodiment of the present inventive concept.

[0065] FIG. 17 is a layout view of one pixel area of an organic light emitting diode display according to an exemplary embodiment of the present inventive concept.

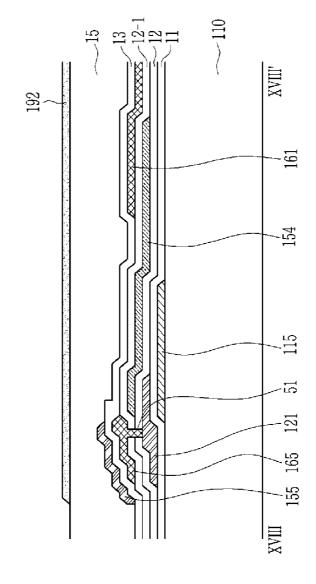

[0066] FIG. 18 is a cross-sectional view taken along a line XVIII-XVIII' in an exemplary embodiment of FIG. 17.

[0067] FIG. 19 is a cross-sectional view taken along a line XIX-XIX' in an exemplary embodiment of FIG. 17.

[0068] FIG. 20 is a cross-sectional view taken along a line XX-XX' in an exemplary embodiment of FIG. 17.

# DETAILED DESCRIPTION OF EXEMPLARY EMBODIMENTS

**[0069]** The present inventive concept will be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments thereof are shown. As those skilled in the art would realize, the described embodiments may be modified in various different ways, all without departing from the spirit or scope of the present invention.

[0070] To clarify embodiments of the present inventive concept, like numbers refer to like elements throughout the specification.

[0071] In addition, the size and thickness of each configuration shown in the drawings are arbitrarily shown for better understanding and ease of description, but embodiments of the present inventive concept are not limited thereto.

[0072] It will be understood that when an element such as a layer, film, region, or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may also be present.

[0073] Further, in this specification, the phrase "on a plane" means viewing a target portion from the top, and the phrase "on a cross-section" means viewing a cross-section formed by vertically cutting a target portion from the side. [0074] Now, a pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept is described with reference to FIG. 1.

[0075] FIG. 1 is an equivalent circuit diagram of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept.

[0076] Referring to FIG. 1, a pixel PX of an organic light emitting diode display includes a plurality of transistors T1, T2, and T3, a storage capacitor Cst, additional capacitors Ca and Cb, and an organic light emitting diode (OLED), which are connected to several signal lines 151, 152, 171, 172, 173, 155 (195), and 156 (196).

[0077] The organic light emitting diode display according to an exemplary embodiment of FIG. 1 shows an organic light emitting diode display used in high resolution (4K or 8K), and two pixels PX are controlled by two data lines 171 and 172 and two scan lines 151 applied with the same signal. [0078] First, the structure of the pixel PX is described.

[0079] A plurality of transistors T1, T2, and T3 included in one pixel PX include a driving transistor T1 (hereinafter referred to as a first transistor), and include a switching transistor T2 (hereinafter referred to as second transistor) connected to a scan line 151, and an initialization transistor T3 (hereinafter referred to as a third transistor or a sensing transistor) connected to a previous scan line 152. In an exemplary embodiment, the third transistor T3 is connected to a signal line that applies a gate-on voltage at different timing from the previous scan line 152.

[0080] The plurality of signal lines 151, 152, 171, 172, 173, 155 (195), and 156 (196) included in one pixel PX may

include the scan line 151, a previous scan line 152, the data lines 171 and 172, an initialization voltage line 173 (hereinafter referred to as a sensing line), a driving voltage line (155 and 195), and a driving low voltage line (156 and 196). [0081] The scan line 151 is connected to a gate driver (not shown) to transmit a scan signal Sn to the second transistor T2. The gate driver may be implemented by a gate driving circuit. The scan line 151 is connected to the pixels PX included in the two rows while coming from the gate driver in one line and being separated into two lines in the display area where the pixels PX are disposed. The scan line 151, which is separated into two lines that receive the same scan signal Sn, is hereinafter also referred to as a pair of scan lines 151.

**[0082]** The previous scan line **152** is connected to the gate driver and transfers the previous scan signal S(n-1) applied to the pixel PX disposed at the previous stage to the third transistor T3. The previous scan line **152** is separated into two lines like the scan line **151** to be connected to the pixels PX included in two rows. The previous scan line **152** is separated into two lines that are applied with the same previous scan signal S(n-1), and is also referred to as a pair of previous scan lines **152**.

[0083] The data lines 171 and 172 are wiring transmitting a data voltage Dm generated from a data driver (not shown), and the two data lines 171 and 172 are formed for one pixel column. The data driver may be implemented by a data driving circuit. For example, data line 171 may transmit a first data voltage D1 and data line 172 may transmit a second data voltage D2. The two data lines 171 and 172 formed for one pixel column are also referred to as a pair of data lines 171 and 172. The pair of data lines 171 and 172 and the pair of scan lines 151 are connected to two pixels PX included in one pixel column. That is, one of two pixels PX included in the pixel column is connected to the first data line 171 and one of the pair of scan lines 151, and the other of the two pixels is connected to the second data line 172 and the other of the pair of scan lines 151. The two adjacent pixels PX included in the pixel column are connected to different data lines 171 and 172 and scan lines 151 of the pair of data lines 171 and 172 and the pair of scan lines 151. Luminance of light emitted from the organic light emitting diode (OLED) (referred to as an organic light emitting element) changes depending on the data voltage Dm provided to the pixel PX along the data lines 171 and 172.

[0084] In an exemplary embodiment, the driving voltage lines 155 and 195 apply a driving voltage ELVDD, and the driving low voltage lines 156 and 196 apply the driving low voltage ELVSS. In an embodiment, the driving voltage ELVDD is higher than the driving low voltage ELVSS. The driving voltage lines 155 and 195 and the driving low voltage lines 156 and 196 according to a present exemplary embodiment include wiring extending in a horizontal direction and wiring extending in a longitudinal direction, and are formed with a mesh structure. Also, the layers of the wiring extending in the horizontal direction and the wiring extending in the longitudinal direction are different from each other so that the reference numeral is also given as different numbers. The voltages applied to the driving voltage lines 155 and 195 and the driving low voltage lines 156 and 196 may be a predetermined voltage, respectively. The driving voltage ELVDD acts as an input voltage to generate an output current from the driving transistor T1, and when the output current is applied to the anode of the organic light emitting diode (OLED), the driving low voltage ELVSS is applied to the cathode electrode of the OLED.

[0085] Hereinafter, a plurality of transistors are described. [0086] First, the driving transistor T1 is a transistor controlling a magnitude of the current output depending on the data voltage Dm applied to the gate electrode, and the output driving current Id is applied to the organic light emitting diode (OLED) such that brightness of the organic light emitting diode (OLED) is controlled depending on the data voltage Dm. For this purpose, the first electrode (an input side electrode) of the driving transistor T1 is disposed to receive the driving voltage ELVDD, and the second electrode (an output side electrode) is connected to the first electrode (hereinafter referred to as an anode or a pixel electrode) of the organic light emitting diode (OLED). Also, the gate electrode of the driving transistor T1 is connected to the second electrode (the output side electrode) of the second transistor T2 to receive the data voltage Dm.

[0087] In an embodiment, the gate electrode of the driving transistor T1 is connected to one electrode of the storage capacitor Cst. The storage capacitor Cst ensures that the data voltage Dm transmitted to the gate electrode of the driving transistor T1 is maintained for one frame period. Therefore, the voltage of the gate electrode of the driving transistor T1 changes depending on the voltage stored in the storage capacitor Cst, and accordingly, the driving current Id output from the driving transistor T1 is changed and is constantly output during one frame period. In an exemplary embodiment, one frame period is a period during which image data is output to all pixels of the display device.

[0088] The driving transistor T1 includes a semiconductor layer in which a channel is disposed. In an exemplary embodiment, the driving transistor T1 further includes an overlapping layer 115 disposed under a portion of the semiconductor layer in which the channel is disposed. The overlapping layer 115 overlaps the channel and the gate electrode of the driving transistor T1, thereby improving a characteristic of the driving transistor T1 and maintaining the voltage of the gate electrode. Since the overlapping layer 115 overlaps the gate electrode, the voltage of the gate electrode is maintained, thereby supplementing the capacitance of the storage capacitor Cst. Hereinafter, a capacitor formed by the overlapping between the overlapping layer 115 and the gate electrode of the driving transistor T1 is referred to as an overlapping capacitor (not shown). The overlapping layer 115 is electrically connected to the second electrode (the output side electrode) of the driving transistor T1, and as a result, the overlapping layer 115 is also connected to the anode of the resultant organic light emitting diode (OLED).

[0089] The second transistor T2 (hereinafter referred to as the switching transistor) is a transistor that receives the data voltage Dm as input to the pixel PX. The gate electrode of the second transistor T2 is connected to the scan line 151, the first electrode of the second transistor T2 is connected to the data line 171, and the second electrode (the output side electrode) of the second transistor T2 is connected to the gate electrode of the driving transistor T1. If the second transistor T2 is turned on depending on the scan signal Sn transmitted through the scan line 151, the data voltage Dm transmitted through the connected data line of a pair of data lines 171 and 172 is transmitted to the gate electrode of the driving transistor T1 and is stored to the storage capacitor Cst.

[0090] The third transistor T3 (hereinafter referred to as the initialization transistor or the sensing transistor) plays a role of initializing the second electrode (the output side electrode) of the driving transistor T1, one electrode of the storage capacitor Cst, and the anode of the organic light emitting diode (OLED). The gate electrode of the third transistor T3 is connected to the previous scan line 152, and the first electrode of the third transistor T3 is connected to the initialization voltage line 173. The second electrode of the third transistor T3 is electrically connected to the second electrode (the output side electrode) of the driving transistor T1, and as a result, is also connected to the anode of the organic light emitting diode (OLED) and the overlapping layer 115.

[0091] The initialization voltage line 173 not only provides an initialization voltage, but is also used as wiring (e.g., a sensing line) for sensing the voltage of the anode connected to the second electrode of the third transistor T3 according to a sensing period. As a result, the third transistor T3 is also referred to as the sensing transistor.

[0092] The operation of the third transistor T3 is now described. The voltage of the anode when the organic light emitting diode (OLED) emits light (an emitting period) is stored on one electrode of the storage capacitor Cst. At this time, the data voltage Dm is stored in the other electrode of the storage capacitor Cst. At this time, if the gate-on voltage is applied to the gate electrode of the third transistor T3, the initialization voltage line 173 operates as a sensing line, and the voltage of the anode is transmitted to a sensing unit (not shown) through the sensing line. Hereinafter, this is referred to as a sensing period. Next, in a reset period among the period in which the gate-on voltage is applied to the gate electrode of the third transistor T3, the initialization voltage line 173 applies the initialization voltage Vint to initialize the voltage of the anode. Hereinafter, this is referred to as an initialization period.

[0093] If the voltage (e.g., a sensing signal SS) detected in the sensing period is different from the voltage of the anode that is expected when it is determined based on the applied data voltage Dm, the data voltage Dm may be modified to be provided to the pixel PX. That is, the characteristic of the driving transistor T1 may be changed, and the organic light emitting diode (OLED) may emit normal light by sensing the change and providing the data voltage Dm corresponding thereto.

[0094] That is, two electrodes of the storage capacitor Cst play a role of maintaining the data voltage Dm and the voltage of the anode (the output electrode voltage of the driving transistor) of the organic light emitting diode (OLED) during one frame period.

[0095] However, since the area occupied by a pixel PX of an organic light emitting diode display of a high resolution and the area for forming a storage capacitor Cst in the pixel PX are small, a storage capacitance may be insufficiently maintained for one frame period.

[0096] Therefore, the pixel PX of the present exemplary embodiment further includes first and second additional capacitors Ca and Cb to have sufficient storage capacitance to maintain the voltage of the anode of the organic light emitting diode (OLED) for one frame period.

[0097] The first additional capacitor Ca has one side electrode connected to the anode of the organic light emitting diode (OLED) and the other side electrode to which the driving voltage ELVDD is applied. That is, the first addi-

tional capacitor Ca plays a role of maintaining the voltage of the anode of the organic light emitting diode (OLED).

[0098] Also, since the second additional capacitor Cb has one side electrode connected to the anode of the organic light emitting diode (OLED) and the other side electrode to which the driving low voltage ELVSS is applied, the second additional capacitor Cb also plays a role of maintaining the voltage of the anode of the organic light emitting diode (OLED).

[0099] Therefore, the capacitor included in one pixel PX has the storage capacitor Cst and the additional capacitors Ca and Cb, thereby ensuring sufficient storage capacitance for maintaining the voltage of the anode of the organic light emitting diode (OLED) during one frame period. Also, according to an exemplary embodiment, an overlapping capacitor formed by the overlapping layer 115 may be further included.

[0100] According to an exemplary embodiment of the inventive concept, the pixel PX further includes only the first additional capacitor Ca or further includes only the second additional capacitor Cb. In addition, the neighboring pixel PXs may have the additional capacitors Ca and Cb of different sizes. In addition, although the capacitance of the first additional capacitor Ca and the capacitance of the second additional capacitor Cb may be different from each other in the adjacent pixels PX, the sum of the capacitances of the two additional capacitors Ca and Cb may be set to be substantially constant.

[0101] The operation of one pixel of the organic light emitting diode display according to an exemplary embodiment of the inventive concept is now described with reference to FIG. 1 and FIG. 2.

[0102] FIG. 2 is a timing diagram of a signal applied to one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept. [0103] In FIG. 2, a signal labeled SCAN is the signal applied to the scan line 151, and a signal labeled SENSING indicates the signal applied to the previous scan line 152.

[0104] First, during a sensing/initial period, the previous scan signal S(n-1) of a high level is supplied to the pixel PX through the previous scan line 152. Then, the third transistor T3 receiving the previous scan signal S(n-1) is turned on. At this time, the voltage stored in the anode of the organic light emitting diode (OLED) is confirmed through the initialization voltage line 173 (the sensing period), and then the voltage of the anode of the organic light emitting diode is changed into the initialization voltage Vint to be initialized. (Initialization period)

[0105] When the characteristic of the driving transistor T1 changes while the driving transistor T1 disposed at each pixel PX has different threshold voltages Vth due to a process dispersion or is operated during a long term by the sensing period, this change is sensed so that the organic light emitting diode (OLED) normally emits light.

[0106] Next, during a data writing period, the scan signal Sn of a high level is supplied to the pixel PX through the scan line 151. The second transistor T2 is turned on by the scan signal Sn of a high level. If the second transistor T2 is turned on, the data voltage Dm is input to the gate electrode of the driving transistor T1 via the second transistor T2, and is stored to one side electrode of the storage capacitor Cst. [0107] The turned-on degree of the driving transistor T1 is determined according to the data voltage Dm applied to the gate electrode, and it outputs the driving voltage ELVDD

which is input to the first electrode to be transmitted to the anode of the organic light emitting diode (OLED).

[0108] The voltage of the anode of the organic light emitting diode (OLED) is stored in the overlapping capacitor or the first and second additional capacitors Ca and Cb as well as the storage capacitor Cst, and is maintained during one frame period.

[0109] In the above, the circuit structure was mainly described through FIG. 1.

[0110] Hereinafter, how the pixel PX according to an exemplary embodiment is implemented is described with reference to FIG. 3 to FIG. 5.

[0111] FIG. 3 is a layout view of a region of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept, and FIG. 4 and FIG. 5 are a cross-sectional view taken along lines IV-IV and V-V in an exemplary embodiment of FIG. 3.

[0112] Referring to FIG. 3 to FIG. 5, in the organic light emitting diode display according to an exemplary embodiment of the inventive concept, the overlapping layer 115, a semiconductor layer (121, 122, and 123), a gate layer (151, 152, 154, 155, and 156), a first data layer (171, 172, 173, 174, 175, 176, 177, and 178), a second data layer (191, 195, and 196), a pixel electrode layer (201 and 206), an organic emission layer 350, and a cathode 310 are respectively formed on the substrate 110, and these layers are insulated from each other by an insulating layer between them unless they are connected by an opening.

[0113] The substrate 110 may be formed as a glass substrate or a flexible substrate containing plastic or polyimide (PI). When the substrate 110 is formed as the flexible substrate, unlike the case of the glass substrate, an additional inorganic insulating layer may be further formed.

[0114] The overlapping layer 115 formed on the substrate 110 is now described. The overlapping layer 115 includes a channel overlapping part overlapping the channel of the driving transistor T1, an extension part disposed under the storage capacitor Cst, and a connection part. The extension part of the overlapping layer 115 overlaps the extension part of a later-described gate electrode 154 to form the overlapping capacitor. The connection part of the overlapping layer 115 is connected to a later-described storage electrode 174 to receive the voltage of the anode. As a result, the overlapping capacitor holding the voltage of the anode is configured.

[0115] A buffer layer 11 covers the substrate 110 and the overlapping layer 115. The buffer layer 11 may be formed of the inorganic insulating material.

[0116] The semiconductor layer (121, 122, and 123) is formed on the buffer layer 11. Each semiconductor layer (121, 122, and 123) includes the channels of the driving transistor T1, the second transistor T2, and the third transistor T3. The semiconductor layer (121, 122, and 123) according to a present exemplary embodiment is formed of an oxide semiconductor. Each semiconductor layer (121, 122, and 123) includes the channel of each transistor T1, T2, and T3 and a source/drain region disposed on both sides of the channel. The source/drain region of each semiconductor layer (121, 122, and 123) is respectively extended and electrically connected to a different layer through an opening. The third semiconductor 123 including the channel of the third transistor T3 includes an extending part extending in the first direction (a transverse direction). The third semiconductor 123 of the third transistor T3 further includes

a protrusion protruded from the extending part. That is, the extending part of the third semiconductor 123 is protruded to be connected to the third semiconductor 123 of the third transistor T3 of the adjacent pixel PX and extends to a position where the initialization voltage line 173 is formed. In the present exemplary embodiment, one initialization voltage line 173 is formed for three pixels PX, and the third semiconductors 123 of the third transistors T3 of three pixels PX are connected to each other to receive the initialization voltage Vint. Here, the extending part of the third semiconductor 123 may be doped to have the same characteristic as a conductor. On the other hand, according to an exemplary embodiment, the extending part of the third semiconductor 123 may be formed through a conductive layer other than the semiconductor layer such as a gate layer.

[0117] A gate insulating layer 12 covers the semiconductor layer (121, 122, and 123) and the buffer layer 11. The gate insulating layer 12 may be formed of the inorganic insulating material.

[0118] The gate layer (151, 152, 154, 155, and 156) is formed on the gate insulating layer 12. The gate layer includes the scan line 151, the previous scan line 152, the gate electrode 154 of the driving transistor T1, the first driving voltage line 155, and the first driving low voltage line 156.

[0119] The scan line 151 extends in the first direction (transverse direction), and includes a protrusion protruding toward a second semiconductor 122 where the channel of the second transistor T2 is disposed. The protrusion of the scan line 151 is the gate electrode of the second transistor T2.

[0120] The previous scan line 152 extends in the first direction (the transverse direction), and passes through the portion of the third semiconductor 123 where the channel of the third transistor T3 is disposed. The part where the previous scan line 152 meets the third semiconductor 123 is the gate electrode of the third transistor T3. However, according to an exemplary embodiment, the previous scan line 152 may further include a structure protruded toward the third semiconductor 123.

[0121] The first driving voltage line 155 and the first driving low voltage line 156 extend in the first direction (the transverse direction) as wiring for applying the driving voltage ELVDD and the driving low voltage ELVSS, respectively. The first driving voltage line 155 and the first driving low voltage line 156 respectively play a role of transmitting the driving voltage ELVDD and the driving low voltage ELVSS in the first direction. Hereinafter, the first driving voltage line 155 and the first driving low voltage line 156 are also referred to as a transverse driving voltage line and a transverse driving low voltage line, respectively.

[0122] The gate electrode 154 of the driving transistor T1 includes the overlapping part overlapping a first semiconductor 121 in which the channel of the driving transistor T1 is disposed and the extension part extending from the overlapping part. The overlapping part of the gate electrode 154 of the driving transistor T1 performs the role of the gate electrode, and the extension part forms one side electrode of the storage capacitor Cst. The extension part of the overlapping layer 115 to form the overlapping capacitor. The gate electrode 154 further includes an extending part extending

from the extension part, and receives the data voltage Dm from the second electrode of the second transistor T2 through the extending part.

[0123] A first interlayer insulating layer 13 covers the gate layer (151, 152, 154, 155, and 156) and the gate insulating layer 12. The first interlayer insulating layer 13 may be formed of the inorganic insulating material.

[0124] The first data layer (171, 172, 173, 174, 175, 176, 177, and 178) is formed on the first interlayer insulating layer 13. The first data layer includes the pair of data lines 171 and 172, the initialization voltage line 173, the storage electrode 174, a driving voltage connection part 175, a driving low voltage connection part 176, a gate electrode connection part 177, and a step removing part 178.

[0125] The pair of data lines 171 and 172 are formed for each pixel column, and extend in a second direction (a longitudinal direction) perpendicular to the first direction. The pair of data lines 171 and 172 are arranged on both sides with respect to the position where the transistors T1, T2, and T3 are formed. One of the pair of data lines 171 and 172 is connected to the second semiconductor 122 of the second transistor T2 through an opening 64, and applies the data voltage Dm to the second transistor T2.

[0126] The initialization voltage line 173 is extended to the second direction like the pair of data lines 171 and 172, and applies the initialization voltage Vint. The initialization voltage line 173 is not formed for every pixel column, and one initialization voltage line 173 is formed for every three pixel columns in the present exemplary embodiment. The initialization voltage line 173 is connected to the extending part of the third semiconductor 123 through an opening 69. The third semiconductor 123 is connected to the third transistor T3 of each pixel PX by the protrusion to sense or initialize the voltage (i.e., the voltage of the anode) of the second electrode of the third transistor T3 of each pixel PX. [0127] The storage electrode 174 has the extension part overlapping the extension part of the gate electrode 154, and includes the extending part extending from the extension part. The extending part of the storage electrode 174 is connected to the second electrode (the output side electrode) of the driving transistor T1, the overlapping layer 115, and the second electrode of the third transistor through openings 63, 61, and 66, respectively. The extension part of the storage electrode 174 overlaps the gate electrode 154 to form the storage capacitor Cst. As shown in FIG. 3, the extension part of the storage electrode 174 and the extension part of the gate electrode 154 occupy a large area within the pixel PX, but the area where the pixel PX is formed is reduced while increasing the resolution, therefore the capacitance of the storage capacitor Cst may be insufficient. To prevent this problem, the overlapping capacitor may be formed by adding the extension part of the overlapping layer 115 overlapping the extension part of the gate electrode 154. In addition, at least one of the additional capacitors Ca and Cb to be discussed below is additionally formed. In an exemplary embodiment, the storage electrode 174 is also electrically connected to the anode described later, so that the voltage of the storage electrode 174 is equal to the voltage of the anode and is initialized every frame period. [0128] The driving voltage connection part 175 as a connection part that applies the driving voltage ELVDD to the first semiconductor 121 of the driving transistor T1 has an island structure. The driving voltage connection part 175 is connected to the first driving voltage line 155 through an opening 83, and is connected to the first semiconductor 121 through an opening 62. Also, the driving voltage connection part 175 extends upward and is connected to the second driving voltage line 195 described later through an opening 82.

[0129] In an exemplary embodiment, the driving low voltage connection part 176 has a linear structure, and facilitates the connection between the second driving low voltage line 196 and the first driving low voltage line 156, which will be described later. That is, the gate layer includes the first driving low voltage line 156, the second data layer includes the second driving low voltage line 196, and the first data layer includes the driving low voltage connection part 176 which is disposed between the gate layer and the second data layer. This structure improves a contact characteristic. According to an exemplary embodiment, the driving low voltage connection part 176 is omitted.

[0130] The gate electrode connection part 177 plays a role of electrically connecting the second electrode of the second transistor T2 and the gate electrode 154 of the driving transistor T1. That is, the gate electrode connection part 177 is connected to the second semiconductor 122 of the transistor T2 through an opening 65, and is connected to the extending part of the gate electrode 154 through an opening 67. According to an exemplary embodiment, since the gate electrode 154 and the second semiconductor 122 may be directly connected, the gate electrode connection part 177 may be omitted.

[0131] The step removing part 178 has the island structure, and is electrically connected to the extending part of the third semiconductor 123 by an opening 68. The step removing part 178 is formed to prevent the overlying second driving voltage line 195 or the second driving low voltage line 196 from being disconnected by the step. According to an exemplary embodiment, the step removing part 178 may be in a floating state, however the step removing part 178 receives the initialization voltage Vint in the present exemplary embodiment.

[0132] A second interlayer insulating layer 14 covers the first data layer (171, 172, 173, 174, 175, 176, 177, and 178) and the first interlayer insulating layer 13. The second interlayer insulating layer 14 may be formed of the inorganic insulating material.

[0133] A second data layer (191, 195, and 196) is formed on the second interlayer insulating layer 14. The second data layer includes an anode connection part 191, the second driving voltage line 195, and the second driving low voltage line 196.

[0134] The anode connection part 191 has the island structure, and is connected to the storage electrode 174 by an opening 81. Since the storage electrode 174 is connected to the second electrode (the output side electrode) of the driving transistor T1 to be electrically connected to the anode, which is one side electrode of the organic light emitting diode (OLED), the anode connection part 191 is formed for this.

[0135] The second driving voltage line 195 extends in the second direction (the longitudinal direction) to transmit the driving voltage ELVDD in the second direction. In an embodiment, the second driving voltage line 195 is wider than the width of one pixel PX. The second driving voltage line 195 is connected to the driving voltage connection part 175 through the opening 82, and connected to the first driving voltage line 155 through the driving voltage con-

nection part 175. Hereinafter, the second driving voltage line 195 is referred to as the longitudinal driving voltage line. In an exemplary embodiment, the second driving voltage line 195 is formed except at the region where the anode connection part 191 is formed according to the position, and has an opening 197 (hereinafter also referred to as an anode connection part opening) corresponding to the anode connection part 191. The second driving voltage line 195 has the structure of which the width is reduced at the portion where the anode connection part 191 is disposed. In an embodiment, the width of the second driving voltage line 195 is greater than the width of the anode 201 formed thereon.

[0136] In an exemplary embodiment, the driving voltage ELVDD has a constant voltage, which is applied by the first driving voltage line 155 in the horizontal direction and by the second driving voltage line 195 in the longitudinal direction, so that the constant voltage is applied at each pixel PX

[0137] The second driving low voltage line 196 is extended in the second direction (the longitudinal direction) to transmit the driving low voltage ELVSS in the second direction, and is spaced apart from the second driving voltage line 195 by a certain distance. Hereinafter, the second driving low voltage line 196 is also referred to as a longitudinal driving low voltage line. The second driving low voltage line 196 is connected to the driving low voltage connection part 176 and the first driving low voltage line 156 through an opening 87. Referring to FIG. 4, the opening 87 is collectively referred to as two openings formed at the same location, where the first opening 87 connects the first driving low voltage line 156 and the driving low voltage connection part 176, and the second opening 87 connects the driving low voltage connection part 176 and the second driving low voltage line 196.

[0138] In an exemplary embodiment, the second driving low voltage line 196 has a width that is equal to the width of one anode 201. In an exemplary embodiment, the second driving low voltage line 196 has a width that is greater than at least half of the width of the anode 201. In addition, the second driving low voltage line 196 has the structure in which the width is partially reduced at the portion where the anode connection part 191 is disposed.

[0139] In an exemplary embodiment, the driving low voltage ELVSS has a constant voltage, which is applied by the first driving low voltage line 156 in the horizontal direction and by the second driving low voltage line 196 in the longitudinal direction, so that the constant voltage may be applied at each pixel PX.

[0140] An upper insulating layer 15 is formed on the second data layer (191, 195, and 196) and the second interlayer insulating layer 14. The upper insulating layer 15 may be formed of an organic insulating material, and have a characteristic of removing and flattening the step.

[0141] The pixel electrode layer is disposed on the upper insulating layer 15, and the pixel electrode layer includes the anode 201 and a cathode connection part 206.

[0142] The anode 201 as one side electrode of the organic light emitting diode (OLED) transmits the current output from the driving transistor T1 to the organic emission layer 350. In order to receive the output current from the driving transistor T1, the anode 201 is connected to the anode connection part 191 by an opening 91 and is connected with

the storage electrode 174 by the opening 81. The size and shape of the anode 201 may be different for each adjacent pixel PX.

[0143] The cathode connection part 206 is a connection part that allows the driving low voltage ELVSS to be applied to the cathode 310, which is the other side electrode of the organic light emitting diode (OLED). The cathode connection part 206 is electrically connected to the second driving low voltage line 196 through an opening 92, and is also electrically connected to the cathode 310 described later.

[0144] A partition 300 is formed between the adjacent anodes 201. The partition 300 has an opening 301 that exposes the anode 201, and the organic emission layer 350 may be disposed within the opening 301.

[0145] The cathode 310 is disposed on the organic emission layer 350 and the partition 300. The partition 300 further includes an opening 302 exposing the cathode connection part 206. The cathode 310 is connected to the cathode connection part 206 through the opening 302, and receives the driving low voltage ELVSS.

[0146] According to the above structure, the second driving voltage line 195 and the second driving low voltage line 196 are formed under and overlapped with anode 201. The part where the anode 201 overlaps the second driving voltage line 195 forms the first additional capacitor Ca, and the part where the anode 201 overlaps the second driving low voltage line 196 forms the second additional capacitor Cb

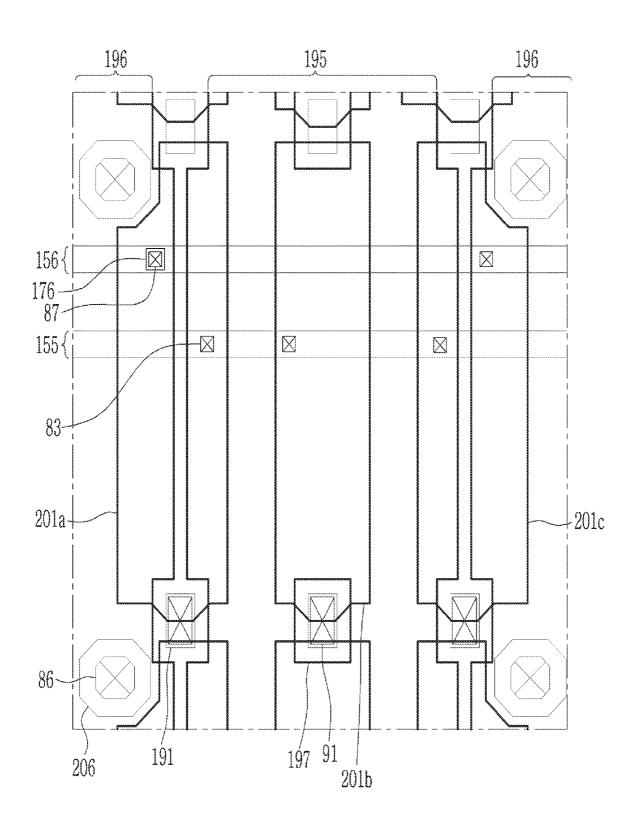

[0147] FIG. 3 to FIG. 5 are complex due to the different constituent elements, so the structure of the additional capacitors Ca and Cb is described through FIG. 6.

[0148] FIG. 6 is a layout view showing only a specific layer among one pixel of an organic light emitting diode display according to an exemplary embodiment of FIG. 3.

**[0149]** FIG. 6 mainly shows the second data layer and the pixel electrode layer, and the first driving voltage line **155** to which the driving voltage ELVDD is applied and the first driving low voltage line **156** to which the driving low voltage ELVSS is applied are additionally shown.

[0150] According to FIG. 6, the anode 201 has different areas for the adjacent pixels PX. The first pixel PX shown on the rightmost side has an anode 201a of which the edge width is reduced due to the cathode connection part 206, and the third pixel PX shown on the leftmost side has an anode 201c of which the edge width is reduced due to the cathode connection part 206. On the other hand, an anode 201b of the second pixel PX disposed at the middle has the angular structure of the corner portion. However, according to an exemplary embodiment, the central part of the anodes 201a and 201c of the first pixel PX and the third pixel PX are narrower than the anode 201b of the second pixel PX. The result thereof is that the capacitance of the additional capacitors of all pixels may be the same.

[0151] In addition, the second pixel PX disposed at the center of the three pixels has only the first additional capacitor Ca as the additional capacitor. That is, the anode 201b of the second pixel PX overlaps only the second driving voltage line 195, so that only the first additional capacitor Ca is formed. In an exemplary embodiment, a part of the anodes 201a and 201c of the first pixel and the third pixel overlaps the second driving low voltage line 196, and a part overlaps the second driving voltage line 195, thereby having both of the first and second additional capacitors Ca and Cb.

**[0152]** However, all three pixels may have additional capacitors Ca and Cb to compensate for the problem of decreasing the capacity of the storage capacitor Cst when the display is adjusted to a high resolution.

[0153] Referring to FIG. 6, the driving voltage ELVDD is applied with a mesh shape through the first driving voltage line 155 and the second driving voltage line 195, and the driving low voltage ELVSS is applied with the mesh shape through the first driving low voltage line 156 and the second driving low voltage line 196. As a result, even if the pixel PX is far from the part where the driving voltage ELVDD and the driving low voltage ELVSS are applied as the display device is large, the constant voltage may be applied.

[0154] Hereinafter, a variation exemplary embodiment of FIG. 3 is described with reference to FIG. 7 and FIG. 8.

[0155] In the exemplary embodiment of FIG. 7 and FIG. 8, unlike FIG. 3, there is a characteristic that an additional opening 198 (hereinafter also referred to as an opening for a parasitic capacitance) is formed in the second driving voltage line 195.

[0156] FIG. 7 is a layout view of a region of one pixel of an organic light emitting diode display according to an exemplary embodiment of the present inventive concept, and FIG. 8 is a layout view showing only a specific layer among one pixel of an organic light emitting diode display according to the exemplary embodiment of FIG. 7.

[0157] Referring to FIG. 8, the additional opening 198 is formed in the second driving voltage line 195 such that the overlapping area of the anode 201 and the second driving voltage line 195 is reduced. In such a case, there may be a drawback in which the capacitance of the first additional capacitor Ca is reduced. However, since the anode 201 overlaps the first data layer or the gate layer, a parasitic capacitance may be formed to compensate for an insufficient capacitance of the storage capacitor Cst. Also, in this case, the second driving voltage line 195 may reduce the signal delay problem caused by the parasitic capacitance caused by being overlapped with the first data layer or the gate layer. [0158] According to an exemplary embodiment, the additional opening 198 formed in the second driving voltage line 195 may be replaced with a plurality of openings.

[0159] Further, according to an exemplary embodiment, the additional opening 198 is also formed in the second driving low voltage line 196.

[0160] As described above, the pixel PX of the organic light emitting diode display according to an exemplary embodiment of the inventive concept has the additional capacitors Ca and Cb, and may overcome the insufficient capacitance of the storage capacitor Cst due to the reduction of the pixel size due to the addition of the overlapping capacitors.

[0161] Hereinafter, the additional capacitor and the overlapping capacitor in another pixel structure will be described.

[0162] FIG. 9 is an equivalent circuit diagram of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept.

[0163] Referring to FIG. 9, the pixel PX of the organic light emitting diode display includes the plurality of transistors T1, T2, and T3, the storage capacitor Cst, the additional capacitors Ca and Cb, and the organic light emitting diode (OLED), which are connected to the several signal lines 151, 152, 171, 173, 155, and 156.

[0164] The organic light emitting diode display according to the exemplary embodiment of FIG. 9 shows an organic light emitting diode display that may be used in a high resolution of 4K. Unlike the exemplary embodiment of FIG. 1, only one data line 171 is formed for one pixel row. In addition, the scan line 151 does not constitute a pair of scan lines receiving the same signal, so only one scan line receives the signal.

[0165] The plurality of transistors T1, T2, and T3 included in one pixel PX include the driving transistor T1, include the switching transistor T2 (i.e., the second transistor) connected to the scan line 151, and the initialization transistor T3 (i.e., the third transistor or the sensing transistor) connected to the previous scan line 152. The third transistor may be connected to the signal line that applies the gate-on voltage at different timing from the previous scan line 152. [0166] The plurality of signal lines 151, 152, 171, 173, 155, and 156 included in one pixel PX may include the scan line 151, the previous scan line 152, the data line 171, the initialization voltage line 173 (referred to as the sensing line), the driving voltage line 155, and the driving low voltage line 156.

[0167] The scan line 151 is connected to a gate driver (not shown) to transfer the scan signal Sn to the second transistor T2

[0168] The previous scan line 152 is connected to the gate driver, and transfer the previous scan signal S(n-1) applied to the pixel PX disposed at a previous stage to the third transistor T3.

[0169] The data line 171 is a wire for transferring the data voltage Dm generated from the data driver (not shown), and one data line 171 is formed for one pixel column. One data line 171 and one scan line 151 select one pixel to input the data voltage Dm. The luminance emitted by the organic light emitting diode (OLED, referred to as an organic light emitting element) is changed depending on the data voltage Dm provided to the pixel PX.

[0170] The driving voltage line 155 applies the driving voltage ELVDD and the driving low voltage line 156 applies the driving low voltage ELVSS. The driving voltage line 155 and the driving low voltage line 156 according to the present exemplary embodiment are wires extending in the longitudinal direction, and are called a longitudinal driving voltage line and a longitudinal driving low voltage line, respectively. In an exemplary embodiment, the voltages applied to the driving voltage line 155 and the driving low voltage line 156 are constant voltages. The driving voltage ELVDD performs a role of the input voltage for generating the output current in the driving transistor T1, and when the output current is applied to the anode electrode of the organic light emitting diode (OLED), the driving low voltage ELVSS is applied to the cathode electrode of the OLED.

[0171] Hereinafter, a plurality of transistors will be described.

[0172] First, the driving transistor T1 is a transistor controlling the magnitude of the current output according to the data voltage Dm applied to the gate electrode, thereby the output driving current Id is applied to the organic light emitting diode (OLED) and the brightness of the organic light emitting diode (OLED) is controlled depending on the data voltage Dm. For this purpose, the first electrode (the input side electrode) of the driving transistor T1 is disposed to receive the driving voltage ELVDD, and the second electrode (the output side electrode) is connected to the first

electrode (hereinafter referred to as the anode or the pixel electrode) of the organic light emitting diode (OLED). In addition, the gate electrode of the driving transistor T1 is connected to the second electrode (the output side electrode) of the second transistor T2 to receive the data voltage Dm. [0173] In an exemplary embodiment, the gate electrode of the driving transistor T1 is connected to one electrode of the storage capacitor Cst. The storage capacitor Cst ensures that the data voltage Dm transmitted to the gate electrode of the driving transistor T1 is maintained for one frame period. Therefore, the voltage of the gate electrode of the driving transistor T1 changes according to the voltage stored in the storage capacitor Cst, and accordingly the driving current Id output from the driving transistor T1 is changed, and is constantly output for one frame period.

[0174] Also, the driving transistor T1 according to an exemplary embodiment further includes the overlapping layer 115 under the semiconductor layer in which the channel is disposed. The overlapping layer 115 overlaps the channel and the gate electrode of the driving transistor T1, thereby playing a role of improving a characteristic of the driving transistor T1 and maintaining the voltage of the gate electrode. Since the overlapping layer 115 overlaps the gate electrode, the voltage of the gate electrode is maintained, thereby supplementing the capacitance of the storage capacitor Cst. Hereinafter, a capacitor formed by an overlapping between the overlapping layer 115 and the gate electrode of the driving transistor T1 is referred to as an overlapping capacitor (not shown). The overlapping layer 115 is electrically connected to the second electrode (the output side electrode) of the driving transistor T1, and as a result, the overlapping layer 115 is also connected to the anode of the resultant organic light emitting diode (OLED).

[0175] The second transistor T2 (hereinafter referred to as the switching transistor) is a transistor that receives the data voltage Dm as input into the pixel PX. The gate electrode of the second transistor T2 is connected to the scan line 151, the first electrode of the second transistor T2 is connected to the data line 171, and the second electrode (the output side electrode) of the second transistor T2 is connected to the gate electrode of the driving transistor T1. If the second transistor T2 is turned on depending on the scan signal Sn transmitted through the scan line 151, the data voltage Dm transmitted through the data line 171 is transmitted to the gate electrode of the driving transistor T1 and is stored to the storage capacitor Cst.

[0176] The third transistor T3 (hereinafter referred to as the initialization transistor or the sensing transistor) plays a role of initializing the second electrode (the output side electrode) of the driving transistor T1, one electrode of the storage capacitor Cst, and the anode of the organic light emitting diode (OLED). The gate electrode of the third transistor T3 is connected to the previous scan line 152, and the first electrode of the third transistor T3 is connected to the initialization voltage line 173. The second electrode of the third transistor T3 is electrically connected to the second electrode (the output side electrode) of the driving transistor T1, and as a result, is also connected to the anode and overlapping layer 115 of the organic light emitting diode (OLED) and the overlapping layer 115.

[0177] The initialization voltage line 173 provides not only the initialization voltage, but is also used as a wire (e.g., a sensing wire) for sensing the voltage of the anode of the OLED connected to the second electrode of the third tran-

sistor T3 during a sensing period. As a result, the third transistor T3 is also referred to as a sensing transistor.

[0178] The operation of the third transistor T3 is now described. The voltage of the anode of the OLED when the organic light emitting diode (OLED) emits light during an emitting period is stored on one electrode of the storage capacitor Cst. At this time, the data voltage Dm is stored in the other electrode of the storage capacitor Cst. At this time, if the gate-on voltage is applied to the gate electrode of the third transistor T3, the initialization voltage line 173 operates as a sensing line, and the voltage of the anode is transmitted to a sensing unit (not shown) through the sensing line. Hereinafter, this is referred to as the sensing period. Next, during reset period among a period in which the gate-on voltage is applied to the gate electrode of the third transistor T3, the initialization voltage line 173 applies the initialization voltage Vint to initialize the voltage of the anode. Hereinafter, this is referred to as the initialization period.

[0179] If the voltage detected in the sensing period is different from the voltage of the anode that is expected when it is determined based on the applied data voltage Dm, the data voltage Dm may be modified to be provided to the pixel PX. That is, the characteristic of the driving transistor T1 may be changed, and the organic light emitting diode (OLED) may emit normal light by sensing the change and providing the data voltage Dm corresponding thereto.

**[0180]** That is, two electrodes of the storage capacitor Cst may play a role of maintaining the data voltage Dm and the voltage of the anode (the output electrode voltage of the driving transistor) of the organic light emitting diode (OLED) during one frame.

[0181] Since the area occupied by a pixel PX and the area for forming a storage capacitor Cst in the pixel PX is small in an organic light emitting diode display of a high resolution, an insufficient storage capacitance may be maintained for one frame period.

**[0182]** Therefore, the pixel PX of at least one exemplary embodiment of the inventive concept further includes first and second additional capacitors Ca and Cb so as to have sufficient storage capacitance to maintain the voltage of the anode of the organic light emitting diode (OLED) for one frame period.

[0183] The first additional capacitor Ca has one side electrode connected to the anode of the organic light emitting diode (OLED) and the other side electrode to which the driving voltage ELVDD is applied, thereby maintaining the voltage of the anode of the organic light emitting diode (OLED).

[0184] Also, since the second additional capacitor Cb has one side electrode connected to the anode of the organic light emitting diode (OLED) and the other side electrode to which the driving low voltage ELVSS is applied, the second additional capacitor Cb also plays a role of maintaining the voltage of the anode of the organic light emitting diode (OLED).

[0185] Therefore, the capacitor included in one pixel PX has the storage capacitor Cst and the additional capacitors Ca and Cb, thereby ensuring sufficient storage capacitance for maintaining the voltage of the anode of the organic light emitting diode (OLED) during one frame period. Also, according to an exemplary embodiment of the inventive concept, an overlapping capacitor formed by the overlapping layer 115 is further included.

[0186] The organic light emitting diode display according to the exemplary embodiment of FIG. 9 receives the same signals as in FIG. 2.

[0187] The operation of the pixel of FIG. 9 is now described with reference to FIG. 2.

[0188] First, during the sensing/initial period, the previous scan signal S(n-1) of a high level is supplied to the pixel PX through the previous scan line 152. Then, the third transistor T3 receiving the previous scan signal S(n-1) is turned on. At this time, the voltage stored in the anode of the organic light emitting diode (OLED) is confirmed through the initialization voltage line 173 (the sensing period), and then the voltage of the anode of the organic light emitting diode is changed into the initialization voltage Vint to be initialized. (Initialization period)

[0189] When the characteristic of the driving transistor T1 changes while the driving transistor T1 disposed at each pixel PX has different threshold voltages Vth due to a process dispersion or is operated during a long term by the sensing period, this change is sensed so that the organic light emitting diode (OLED) normally emits light.

[0190] Next, during the data writing period, the scan signal Sn of a high level is supplied to the pixel PX through the scan line 151. The second transistor T2 is turned on by the scan signal Sn of a high level. If the second transistor T2 is turned on, the data voltage Dm is input to the gate electrode of the driving transistor T1 via the second transistor T2, and is stored to one side electrode of the storage capacitor Cst.

[0191] The turned-on degree of the driving transistor T1 is determined according to the data voltage Dm applied to the gate electrode, and it outputs the driving voltage ELVDD which is input to the first electrode to be transmitted to the anode of the organic light emitting diode (OLED).

[0192] The voltage of the anode of the organic light emitting diode (OLED) is stored in the additional capacitors Ca and Cb or the overlapping capacitor as well as the storage capacitor Cst, and is maintained during one frame period.

[0193] In the above, the circuit structure was mainly described through FIG. 9.

[0194] Hereinafter, how the pixel PX according to an exemplary embodiment is implemented is described with reference to FIG. 10 to FIG. 12.

[0195] FIG. 10 is a layout view of a region of one pixel of an organic light emitting diode display according to an exemplary embodiment of the inventive concept, and FIG. 11 and FIG. 12 are cross-sectional views taken along lines XI-XI and XII-XII in an exemplary embodiment of FIG. 10. [0196] Referring to FIG. 10 to FIG. 12, in the organic light emitting diode display according to an exemplary embodiment, the overlapping layer 115, the semiconductor layer (121, 122, and 123), the gate layer (151, 152, 153, 154, 157, and 158), a second gate layer (the storage electrode 161), the first data layer (171, 173, 155, 156, 182, 183, 184, and 185), the pixel electrode layer (192, 192-1, and 196), the organic emission layer (not shown), and the common electrode (not shown) are formed on the substrate 110, respectively, and these layers are insulated from each other by an insulating layer between them unless they are connected by an open-

[0197] The substrate 110 may be formed as a glass substrate or a flexible substrate containing plastic or polyimide (PI). When the substrate 110 is formed as the flexible

substrate, unlike the case of the glass substrate, an additional inorganic insulating layer may be further formed.

[0198] The overlapping layer 115 formed on the substrate 110 is now described. The overlapping layer 115 includes an overlapping part overlapping the channel of the driving transistor T1 and a connection part. The connection part of the overlapping layer 115 is connected to a later-described storage electrode 161. Since the storage electrode 161 has the voltage of the anode of an OLED, the overlapping layer 115 also has the voltage of the anode.

[0199] The buffer layer 11 covers the substrate 110 and the overlapping layer 115. The buffer layer 11 may be formed of the inorganic insulating material.

[0200] The semiconductor layer (121, 122, and 123) is formed on the buffer layer 11. Each semiconductor layer (121, 122, and 123) includes the channels of the driving transistor T1, the second transistor T2, and the third transistor T3. The semiconductor layer (121, 122, and 123) according to an exemplary embodiment is formed of an oxide semiconductor. Each semiconductor layer (121, 122, and 123) includes the channel of each transistor T1, T2, and T3, and the source/drain region disposed on both sides of the channel. The source/drain region of each semiconductor layer (121, 122, and 123) is respectively extended and electrically connected to the different layer through the opening.

[0201] The gate insulating layer 12 covers the semiconductor layer (121, 122, and 123) and the buffer layer 11. The gate insulating layer 12 may be formed of an inorganic insulating material.

[0202] The gate layer (151, 152, 153, 154, 157, and 158) is formed on the gate insulating layer 12. The gate layer includes the scan line 151, the previous scan line 152, an initialization voltage transmitting part 153, the gate electrode 154 of the driving transistor T1, a gate electrode 157 of the second transistor T2, and a gate electrode 158 of the third transistor T3.

[0203] The scan line 151 extends in the first direction (the transverse direction), and the previous scan line 152 also extends in the first direction (the transverse direction).

[0204] The initialization voltage transmitting part 153 has a long island shape in the first direction. The initialization voltage transmitting part 153 is a structure for connecting the initialization voltage line 173 formed for a predetermined number of pixel columns and a plurality of pixels. That is, the initialization voltage transmitting part 153 passes an adjacent pixel PX and extends to a position where the initialization voltage line 173 is formed. In the present exemplary embodiment, one initialization voltage line 173 is formed for each three pixels PX.

[0205] The gate electrode 154 of the driving transistor T1 includes an overlapping part overlapping the first semiconductor 121 in which the channel of the driving transistor T1 is disposed, an extension part extended from the overlapping part, and an extending part connected to the second semiconductor 122 of the second transistor T2. In an exemplary embodiment, only the overlapping part of the gate electrode 154 of the driving transistor T1 performs the role of the gate electrode, and the extension part forms one side electrode of the storage capacitor Cst. The extension part of the overlapping layer 115 to form an overlapping capacitor. The extending part of the gate electrode 154 is connected to the second semiconductor 122 of the second transistor T2 through an

opening 74, and receives the data voltage Dm from the second electrode of the second transistor T2.